In our examples, we include the sign bit: thus Q4.4 is from -8 to 7.9375 (7 + 15/16): we discuss range later in this post. ProTip: Some sources include the sign bit in i, but others do not. We’ll mostly use Q4.4 in this post to keep the examples manageable. 0100.1100 has four integer and four fractional bits, so is Q4.4. To express the number of integer and fractional bits we use Q number format: Qi.f where i is the number of integer bits and f is the number of fractional bits. See later in this post if you have existing integers you need to convert to fixed point. We’re choosing to interpret the value as being fixed point, but from an FPGA logic point of view, it’s just an 8-bit integer: provided we are consistent in the position of the fixed point we’ll get the expected result from mathematical operations. Or, with a handy point to mark the fractional part: 0100.1100. In binary terms this can be visualized as: We can do the same thing in binary and use the bits to represent any powers of two we like.įor example, we can think of 4.75 as being 4 + 1/2 + 1/4. 1001 is one thousand and one, whereas 10.01 is ten and one hundredth. With decimal numbers, we’re used to the idea of using a decimal separator, a point or comma, to separate integer and fractional parts. In a regular binary integer, the bits represent powers of two, with the least significant bit being 1.įor example, decimal 13 is 1101 in binary: 8 + 4 + 1 = 13. There are also posts on division, square root, and sine & cosine.

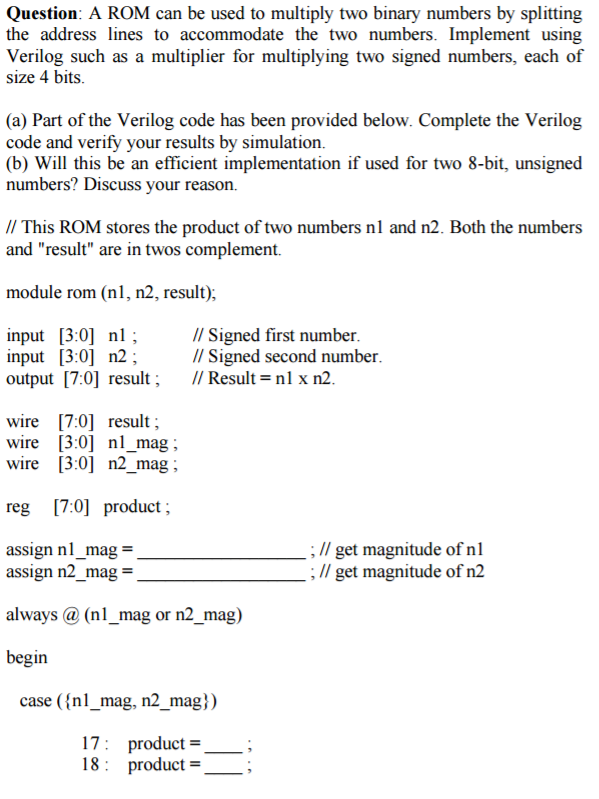

VERILOG SIGNED MULTIPLY SERIES

This post is part of a series of handy recipes to solve common FPGA development problems. Furthermore, most FPGAs have dedicated DSP blocks that make multiplication and addition of integers fast we can take advantage of that with a fixed-point approach.

You could use a library or IP block, but simple fixed point maths can often get the job done with little effort. Sometimes you need more precision than integers can provide, but floating-point computation is not trivial (try reading IEEE 754).

0 kommentar(er)

0 kommentar(er)